Synopsys IP Technical Bulletin: USB High Speed Inter-Chip (HSIC) IP: What is it? And why should I use it?

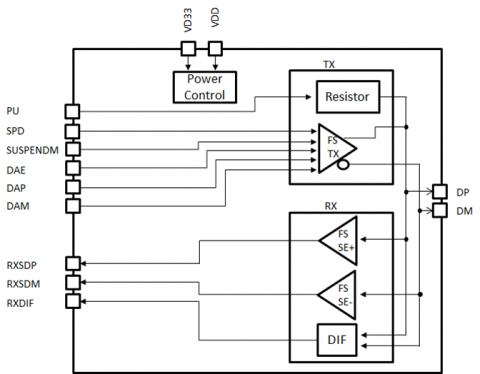

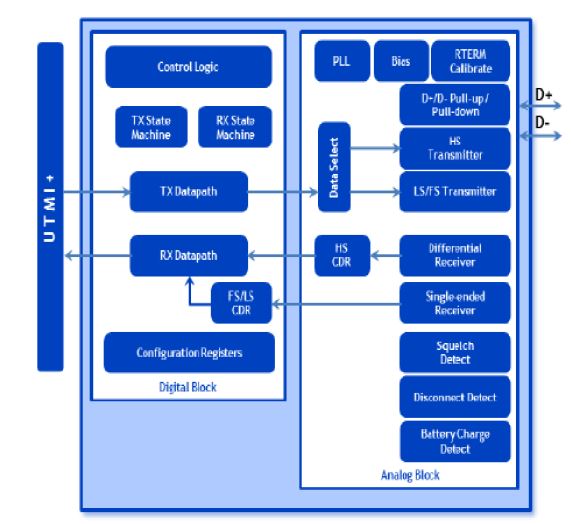

Block diagram of UFP type-C USB 2.0 without PD The USB 2.0 physical... | Download Scientific Diagram

Archimago's Musings: MEASUREMENTS: Computer USB port noise, USB hubs and the 8kHz PHY Microframe Packet Noise